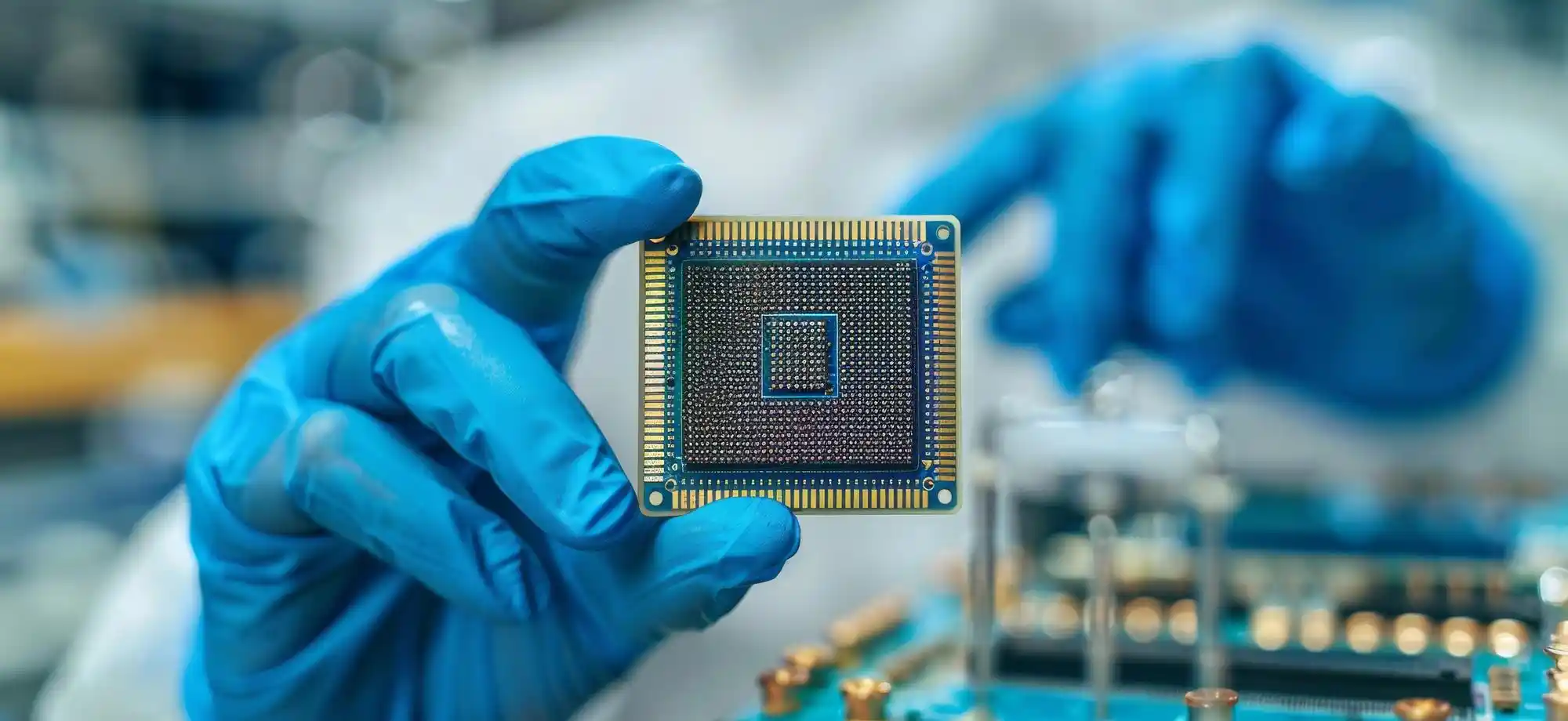

IoT controllers to high-performance Linux capable cores—all from the same codebase!

Overview

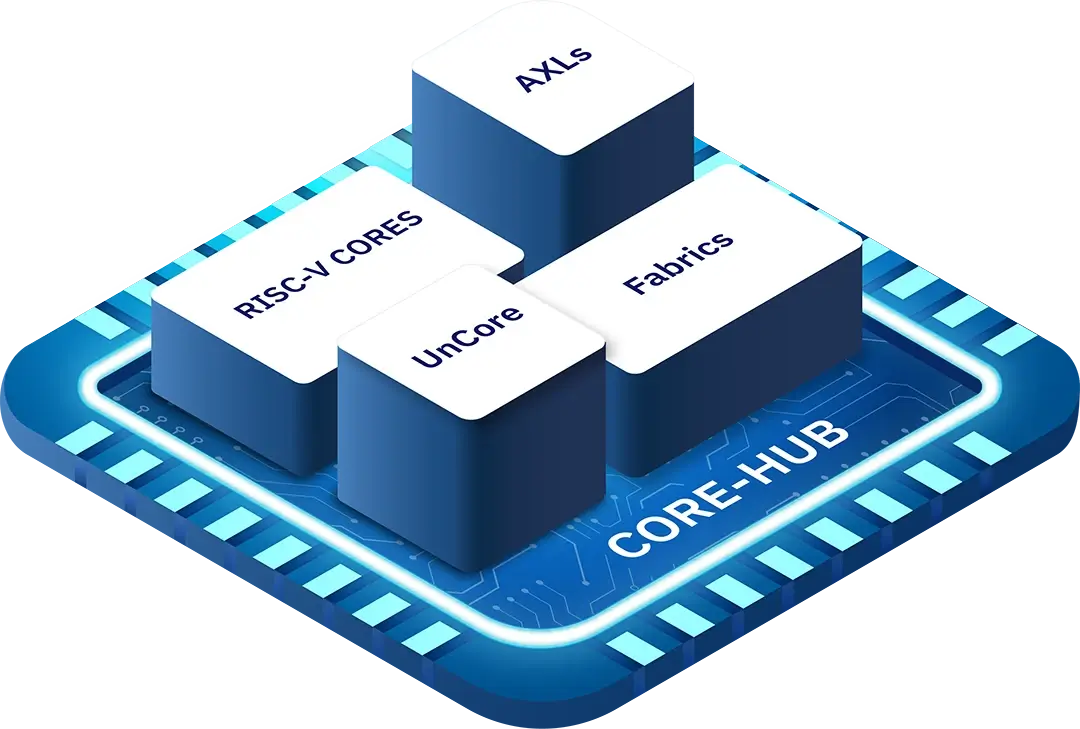

The Core Generator, an automated toolchain, allows users to configure core components. It produces a synthesizable Core-hub instance, along with fabric, uncore, and accelerators. Leveraging RISCV-CONFIG technology, users have fine-grain control over architectural choices, translated to RTL by InCore's Core Generators.

Core-hubs: Your quickstart to efficient SoC development!

Customizable RISC-V cores + versatile interconnect fabrics + standard RISC-V UnCore components + performance-enhancing accelerators.

RISC-V Cores

Azurite Series

Features

- 2-stage in-order 64/32-bit processor

- Optimized for low-power and resource-constrained applications

- Mid-range compute systems: 150-300 MHz

- Supports RV[64|32]IMACUBP ISA with PMP support

- JTAG-based debugging with non-invasive architecture

- Alternative to ARM Cortex M0-M4

Calcite Series

Features

- 5-stage in-order 64/32-bit RISC-V processor

- Multi-core capable with Linux and secure L4 support

- Mid-range compute systems: 500-800 MHz

- Supports RV[64|32]IMAFDCSU [HBP] ISA with MMU & PMP

- IEEE-754 compliant single & double precision floating-point units

- Alternative to ARM Cortex A5/A35

Dolomite Series

Features

- 8-9 stage superscalar 64-bit RISC-V processor (Dual issue)

- High-performance compute: 800 MHz – 1.5 GHz

- Full RISC-V profile compliance, including RVA22H64

- Virtualization support with hypervisor extension

- Integrated integer multiple/divide units & advanced branch prediction

- Alternative to ARM Cortex A5x series

Nexus Series

Azurite Nexus

Key Features

Robust tech stack

We use BSV, Python, eUVM to achieve rapid design space exploration & prototyping capabilities within the Core-hubs.

Massive configurability

Baseline cores-hubs can further be configured & finetuned at the ISA & uarch levels to meet PPA targets.

Holistic collaterals

Automated generation of Documentation, Physical Design collaterals, FPGA collaterals, ASIC collaterals and Software Toolchain, ensuring rapid design and integration into the SoC.

High quality IP

Core-hubs feature a highly configurable verification environment utilizing novel tech such as eUVM and ASM generators to create comprehensive test cases for maximum IP coverage.

sales enquiry